在以人工智能、高性能计算为代表的新需求驱动下,先进封装应运而生,发展趋势是小型化、高集成度,历经直插型封装、表面贴装、面积阵列封装、2.5D/3D封装和异构集成四个发展阶段。

先进封装开辟了 More-than-Moore的集成电路发展路线,能够在不缩小制程节点的背景下,仅通过改进封装方式就能提升芯片性能,还能够打破“存储墙”和“面积墙”。

先进封装也称为高密度封装,具有引脚数量较多、芯片系统较小和高集成化的特点。先进封装属于中道工序,包括清洗、溅射、涂胶、曝光、显影、电镀、去胶、刻蚀、涂覆助焊、回炉焊接、清洗、检测等一系列步骤。与传统的后道封装测试工艺不同,先进封装的关键工艺需要在前道平台上完成,是前道工序的延伸。

下面我们简单了解几种先进封装技术。

1.FOWLP

FOWLP (Fan-out Wafer Level Package)是WLP(Wafer Level Package)的一种,因此我们需要先了解WLP晶圆级封装。晶圆级封装可分为两大类型:扇入型WLCSP(Fan-In Wafer Level Chip Scale Package, Fan-In WLCSP)和扇出型WLCSP(Fan-Out Wafer Level Chip Scale Package, Fan-Out WLCSP)。

因为封装完成后再进行切割分片,因此,封装后的芯片尺寸和裸芯片几乎一致,因此也被称为CSP(Chip Scale Package)或者WLCSP(Wafer Level Chip Scale Packaging),此类封装符合消费类电子产品轻、小、短、薄化的市场趋势,寄生电容、电感都比较小,并具有低成本、散热佳等优点。

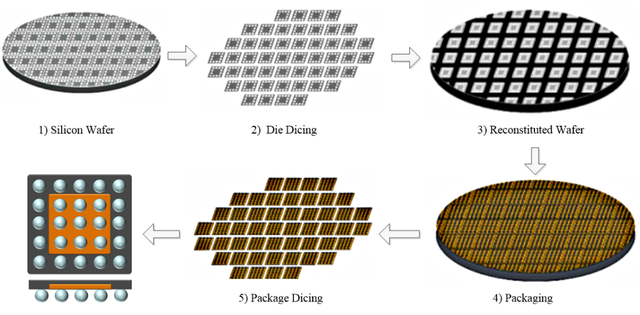

FOWLP,由于要将RDL和Bump引出到裸芯片的外围,因此需要先进行裸芯片晶圆的划片分割,然后将独立的裸芯片重新配置到晶圆工艺中,并以此为基础,通过批量处理、金属化布线互连,形成最终封装。FOWLP封装流程如下图所示。

无论是采用Fan-in还是Fan-out,WLP晶圆级封装和PCB的连接都是采用倒装芯片形式,芯片有源面朝下对着印刷电路板,可以实现最短的电路径,这也保证了更高的速度和更少的寄生效应。另一方面,由于采用批量封装,整个晶圆能够实现一次全部封装,成本的降低也是晶圆级封装的另一个推动力量。

下载:算力时代来临,Chiplet先进封装大放异彩

FOPLP采用了PCB上的生产技术进行RDL的生产,其线宽、线间距目前均大于10um,采用SMT设备进行芯片和无源器件的贴装,由于其面板面积远大于晶圆面积,因而可以一次封装更多的产品。相对FOWLP,FOPLP具有更大的成本优势。目前,全球各大封装业者包括三星电子、日月光均积极投入到FOPLP 制程技术中。

2.EMIB

EMIB(Embedded Multi-Die Interconnect Bridge)嵌入式多芯片互连桥先进封装技术是由英特尔提出并积极应用的,和前面描述的3种先进封装不同,EMIB是属于有基板类封装,因为EMIB也没有TSV,因此也被划分到基于XY平面延伸的先进封装技术。

和硅中介层(interposer)相比,EMIB硅片面积更微小、更灵活、更经济。EMIB封装技术可以根据需要将CPU、IO、GPU甚至FPGA、AI等芯片封装到一起,能够把10nm、14nm、22nm等多种不同工艺的芯片封装在一起做成单一芯片,适应灵活的业务的需求。

通过EMIB方式,KBL-G平台将英特尔酷睿处理器与AMD Radeon RX Vega M GPU整合在一起,同时具备了英特尔处理器强大的计算能力与AMD GPU出色的图形能力,并且还有着极佳的散热体验。这颗芯片创造了历史,也让产品体验达到了一个新的层次。

3.CoWoS

HBM的高密度连接和短互联间距,要求台积电的CoWoS封装技术,是 2.5D封装技术。。CoWoS是台积电于2012年研发的一种2.5D集成封装技术,可分为CoW和oS两步,CoW(chip on wafer)是将计算核心、I/O die、HBM等芯片封装在硅中介层上;然后再把CoW芯片整体封装在基板(Substrate)上,即oS(onsubstrate)环节。CoWoS可以节省空间,实现HBM所需的高互联密度和短距离连接;还能将不同制程的芯片封装在一起,在满足AI、GPU等加速运算的需求的同时控制成本。目前所有先进的 Al计算芯片都使用HBM,而几乎所有HBM都封装在CoWoS上。

4.HBM

HBM(High-Bandwidth Memory )高带宽内存,主要针对高端显卡市场。HBM使用了3D TSV和2.5D TSV技术,通过3D TSV把多块内存芯片堆叠在一起,并使用2.5D TSV技术把堆叠内存芯片和GPU在载板上实现互连。下图所示为HBM技术示意图。

HBM目前有三个版本,分别是HBM、HBM2和HBM2E,其带宽分别为128 GBps/Stack、256 GBps/Stack和307 GBps/Stack,最新的HBM3还在研发中。

5.SoICSoIC也称为TSMC-SoIC,是一项新技术——集成片上系统(System-on-Integrated-Chips),预计在2021年,台积电的SoIC技术就将进行量产。

究竟什么是SoIC?所谓SoIC是一种创新的多芯片堆栈技术,能对10纳米以下的制程进行晶圆级的集成。该技术最鲜明的特点是没有凸点(no-Bump)的键合结构,因此具有有更高的集成密度和更佳的运行性能。

SoIC包含CoW(Chip-on-wafer)和WoW(Wafer-on-wafer)两种技术形态,从TSMC的描述来看,SoIC就一种WoW晶圆对晶圆或CoW芯片对晶圆的直接键合(Bonding)技术,属于Front-End 3D技术(FE 3D),而前面提到的InFO和CoWoS则属于Back-End 3D技术(BE 3D)。TSMC和Siemens EDA(Mentor)就SoIC技术进行合作,推出了相关的设计与验证工具。

3D封装工艺介绍

下图是3D IC和SoIC集成的比较。

具体的说,SoIC和3D IC的制程有些类似,SoIC的关键就在于实现没有凸点的接合结构,并且其TSV的密度也比传统的3D IC密度更高,直接通过极微小的TSV来实现多层芯片之间的互联。如上图所示是3D IC和SoIC两者中TSV密度和Bump尺寸的比较。可以看出,SoIC的TSV密度要远远高于3D IC,同时其芯片间的互联也采用no-Bump的直接键合技术,芯片间距更小,集成密度更高,因而其产品也比传统的3D IC有更高的功能密度。

6.X-Cube

X-Cube(eXtended-Cube)是推出的一项3D集成技术,可以在较小的空间中容纳更多的内存,并缩短单元之间的信号距离。

X-Cube用于需要高性能和带宽的工艺,例如5G,人工智能以及可穿戴或移动设备以及需要高计算能力的应用中。X-Cube利用TSV技术将SRAM堆叠在逻辑单元顶部,可以在更小的空间中容纳更多的存储器。

从X-Cube技术展示图可以看到,不同于以往多个芯片2D平行封装,X-Cube 3D封装允许多枚芯片堆叠封装,使得成品芯片结构更加紧凑。芯片之间采用了TSV技术连接,降低功耗的同时提高了传输的速率。该技术将会应用于最前沿的5G、AI、AR、HPC、移动芯片以及VR等领域。

X-Cube技术大幅缩短了芯片间的信号传输距离,提高数据传输速度,降低功耗,并且还可以按客户需求定制内存带宽及密度。目前X-Cube技术已经可以支持7nm及5nm工艺,三星将继续与全球半导体公司合作,将该技术部署在新一代高性能芯片中。

先进封装对芯片的提升作用包括五个方面:一是实现芯片封装小型化、高密度化、多功能化;二是降低产品功耗、提升产品带宽、减小信号传输延迟;三是可实现异质异构的系统集成;四是延续摩尔定律,提升产品性能的有效途径;五是降低先进节点芯片的设计复杂度和制造成本,缩短开发周期、提高产品良率。