事实上,用这种混合维异质结构以及不同载流子类型的异质-2D层构建的垂直互补场效应晶体管(CFETs)最近已经得到了证明。

然而,到目前为止,在二维半导体中缺乏一种可控的掺杂方案(特别是p掺杂的WSe2和MoS2),最好是稳定和无损的方式,这极大地阻碍了互补逻辑电路的自下而上缩放。

在此,来自中山大学&北京大学的侯仰龙、 中国科学院大学的周武、辽宁省材料研究院的王汉文、山西大学的韩拯以及中国科学院金属研究所&辽宁省材料研究院的李秀艳等研究者表明,通过将过渡金属二硫族化合物,如MoS2,置于范德华(vdW)反铁磁绝缘体氯氧化铬(CrOCl)上,MoS2中的载流子极性可以通过强vdW界面耦合很容易地从n型重新配置为p型。相关论文以题为“Van der Waals polarity-engineered 3D integration of 2D complementary logic”于2024年05月29日发表在Nature上。

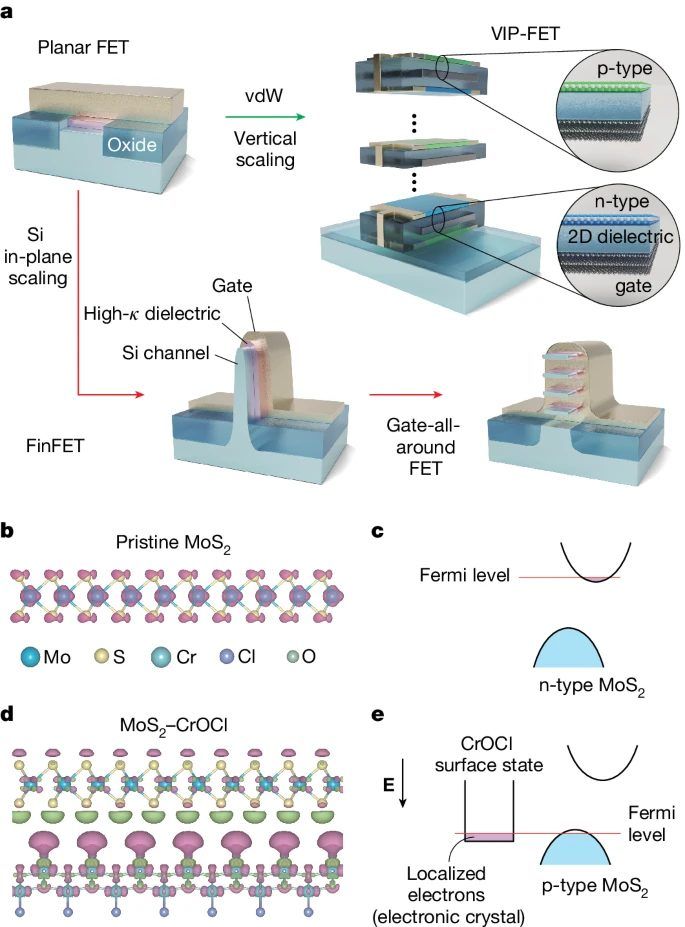

事实上,几十年来,从第一个平面场效应晶体管(FET)到FinFET,再到最先进的栅极全方位FET,硅半导体的缩放一直遵循平面内策略,如图1a所示,而实现3D可积性仍然极具挑战性。

虽然电极的三维互连,已经在现代硅集成电路中得到了广泛的应用,但基本的逻辑门仍然局限于硅衬底的表面,不能排列成多层。其他两个芯片的面对面结合的尝试需要超高精度的对准,并且在z维度上的空间增益不是那么令人满意。

同时,多层3D闪存(3D NAND)由水平和垂直位和字线之间的正交交叉结(形成浮栅存储器)组成,但不满足电路自由设计的需要。

最近,将vdW半导体堆叠成3D垂直电路一直是人们不断努力追求的目标。相当大的带隙和无悬键表面,加上高载流子迁移率和最终尺度(小于1nm)的优秀静电控制,使二维(2D)半导体成为垂直3D集成的理想候选者。

据预测,先进的单片3D集成电路结构具有快速的层对层信号传输和高效的散热,将提供更高的集成密度。然而,在应用方面,由于难以获得n型和p型极性的可控掺杂,2D半导体的3D集成电路在很大程度上受到限制,这是互补逻辑的基础。

迄今为止,在使用二维半导体构建的垂直互补场效应晶体管(CFETs)中已经实现了有限数量的例子,例如混合维异质结构和具有不同载流子极性的异质-2D层,其中已经证明了最多两个垂直互补逻辑层。

事实上,虽然n型2D半导体在电性能方面正在迅速发展,但对于WSe2和MoS2等2D半导体,只有少数p掺杂策略是已知的,使用的方法包括化学掺杂,接触工程或氧化物涂层。

请注意,这些掺杂方法可能存在不均匀性或载流子迁移率降低的问题,并且很少有物理上能够实现三维互补逻辑的多层垂直组装。

在这里,研究者设计了一种简单的非破坏性掺杂方法,通过vdW界面耦合以可控的方式重新配置二维半导体的载流子极性。

研究者发现,与通常表现为n型的过渡金属二硫化物(TMDs)(包括MoS2、WSe2和MoSe2)与少层CrOCl界面不同,TMDs系统地转变为p型,并表现出优异的空气稳定性。

密度泛函理论(DFT)计算表明,这种界面耦合引起的极性反转是电荷从TMDs转移到CrOCl的结果,随后在CrOCl的表面状态发生了微妙的e-e相互作用,这应该是TMDs与具有高功函数和表面带足够大有效质量的层状绝缘体之间的界面上的普遍效应。

以MoS2为例,由于具有原子清洁的界面,MoS2-CrOCl杂化材料的最大室温空穴迁移率约为425 cm2 V−1 s−1,开/关比超过106。

此外,研究者通过选择性地堆叠vdW栅极、介电层和半导体层的模块来构建n和p掺杂的逻辑单元,有或没有界面耦合层,定义为垂直反极化场效应晶体管(VIP-FETs)。

因此,研究者的掺杂策略可以用于垂直制造自补充逻辑器件,为半导体电路的先进3D集成的垂直缩放路线(图1a)提供了线索。

图2 MoS2-CrOCl互补场效应管的电学性能。

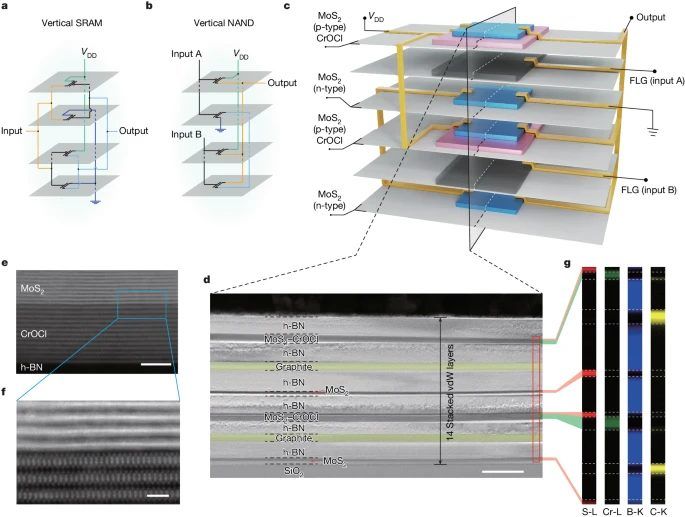

图3 3D集成逻辑门具有十多个vdW层。

图4 面向未来3D集成二维半导体互补逻辑。

综上所述,研究表明,通过将TMDs (MoS2, WSe2和MoSe2)堆叠在vdW绝缘体CrOCl上,可以有效地将主导载流子类型从电子调制到空穴。

第一性原理计算进一步揭示了这种行为可能源于强vdW界面耦合。这表明了门可调谐带对准、电荷转移和e-e相互作用的协同效应,这可能与半导体TMDs的传统p掺杂策略有本质上的不同。

值得注意的是,类似的机制已经导致了先前在石墨烯-CrOCl系统中报道的许多奇异的量子电子态。基于该方法制备的FETs具有优异的电学性能,通/关比达到106,在MoS2中提取的室温空穴迁移率达到425 cm2 V−1 s−1,具有出色的长期空气稳定性。

此外,基于该掺杂方法,实现了先进的3D逻辑电路,如垂直构建的6层vdW逆变器、14层vdW的NANDs和14层vdW的SRAMs,证实了该vdW界面耦合诱导的p型掺杂,可能是设计未来垂直缩放的有效策略,以实现先进逻辑电路的超高3D集成。

【参考文献】

Guo, Y., Li, J., Zhan, X. et al. Van der Waals polarity-engineered 3D integration of 2D complementary logic. Nature (2024).

国内学术评价体系非常糟糕!严格来说,我们基本没有自己的学术评价与发表体系!所有必须依托国外杂志体系!这是非常值得深思与反思的!

把cns文章当成顶级科研成果对中国科研来说是非常危险的!因为cns 三大杂志是西方财团控制的!