铜片夹扣键合QFN 功率器件封装技术

霍炎 吴建忠

(上海交通大学 无锡华润安盛科技有限公司)

摘要:

铜片夹扣键合工艺是一种替代传统引线键合中多引线或者粗引线键合的新工艺,其工艺产品本身具有一定性能优势,并且随着其技术应用的拓展,铜片夹扣键合产品结构变得多样化。针对铜片夹扣键合封装产品的结构设计以及工艺设计发展方向进行了研究,分析了铜片夹扣键合产品的性能优势,以及铜片夹扣键合不同阶段产品的结构特性与发展趋势;依据封装产品发展需求,总结出铜片夹扣键合产品结构未来的发展方向以及发展中面临的瓶颈问题,通过对其封装工艺、结构与材料分析给出对应的解决策略。

1 引言

QFN(Quad Flat No-lead Package,方形扁平无引脚封装)是表面贴装型封装形式之一,因其结构设计自由度高、新品开发周期短、开发成本低、最终产品表贴占板面积小的特点,被广泛应用于工业半导体电源管理元件领域。低导通电阻(RDSON)是功率元器件的重要特性,这种特性有利于降低元器件导通损耗,降低元器件使用温升,提升电源类元件整体效率。随着晶圆制造加工能力与结构特性的不断变革,芯片本身的阻抗变得越来越低,封装体附加的阻抗在元器件总阻抗中的比重变得越来越大,越来越明显[1],因此各种降低封装阻抗的封装工艺结构被广泛开发出来,从引线键合到区域焊接也是元器件封装发展的必然趋势[2]。

铜片夹扣键合(Copper Clip)工艺作为一种取代传统引线键合工艺的新型工艺,被越来越多地应用在半导体分立器件以及功率元器件中。传统引线键合会产生寄生电感、电阻并增加线路延迟,限制热传导,铜片夹扣键合相比传统的引线键合方式提升了电流传输能力,提高了产品整体效率,降低了元器件功耗,提升了产品的散热性能,降低封装寄生参数,且其工艺简单,综合成本相对低廉。铜片夹扣键合工艺被广泛应用于低压大电流元器件上,其终端产品有网络服务器、充电器、笔记本、配置器高端显卡等,这些产品对元件散热、效率要求较高。

虽然铜片夹扣键合工艺对功率器件的诸多性能有着明显的提升优势,但这种工艺并未在国内得到广泛的推广与使用,其主要原因有以下几点。

首先,国内功率器件市场定位在低端应用市场,铜片夹扣键合工艺带来的性能优势尚无法在其终端产品中得以体现,但随着国内功率器件设计水平的提高,其市场也会逐渐向高功率、大电流器件延伸,铜片夹扣键合工艺所带来的性能优势变得不可或缺。

其次,铜片夹扣键合产品设计需要与新品设计相结合,两者相辅相成,因此这种产品多被国外IDM 厂所垄断,而且铜片夹扣键合中关键材料焊接铜片结构的设计,对产品工艺良率以及产品性能起到决定性作用,国内针对这种工艺的设计人才较少,这也使得国内设计公司在开发新产品的过程中无法从封装厂得到足够的支持与帮助。

本文通过描述与比较,对铜片焊接产品的性能优势、工艺设计难点以及工艺发展的挑战做了逐一分析。

2 夹扣键合封装技术优势分析

夹扣键合封装对器件性能优势的提升主要体现在以下几个方面:首先夹扣键合封装技术提升器件的电流承载能力,其次铜片夹扣键合降低器件的导通电阻,再次夹扣键合封装技术提升器件的板级可靠性。同时铜片夹扣键合封装也大大提升了封装效率,有效降低了产品加工周期及加工成本。

2.1 夹扣键合封装技术提升器件的电流承载能力

随着大电流传输能力的发展,传统引线键合工艺已不能满足单位可通电流能力的需求,而铜片夹扣键合工艺有效提升了器件的通流能力,图1 为DFN 8×8产品不同封装形式的对比图,其中传统引线键合方法因为空间限制,只能键合29 根直径50 μm 的铜线,其加总通流截面积为0.057 mm2,而铜片夹扣键合产品通过设计其通流截面积为0.358 mm2,是引线键合产品的6 倍。

两种封装方式的最大可通电流如表1 所示,其中铜线键合产品每根铜线的最大通流能力在2.0~2.1 A[3],29 根引线加总最大通流能力为60 A,铜片夹扣键合产品最大通流能力为350 A。

2.2 铜片夹扣键合降低器件导通电阻

伴随着芯片表面焊接面积与截面积的提升,铜片夹扣键合工艺有效降低了产品的封装导通电阻,相比于铜线或者铝线键合工艺,其互联导通电阻下降幅度高达50%,在相同的电压电流输出条件下,器件的导通损耗也相应降低,以图1 中DFN8×8 器件为例, 10V、20 A 测量条件下2 种产品实际测量导通电阻如表2所示,其中引线键合产品平均6.54 mΩ,铜片夹扣键合产品平均4.75 mΩ,平均导通电阻降低30%。

2.3 夹扣键合封装技术降低器件热阻[4]

降低封装热阻有利于降低器件温升,提升器件的使用寿命。因夹扣键合封装技术可以有效地将器件工作时产生的热量通过铜片带到PCB 层,这种封装工艺相比于传统的引线键合工艺散热面积更大;与此同时,因铜片面积的增大,电源器件散热更快、更均匀,有效降低器件温升,表3 所示为相同芯片、相同封装外形电子元器件的实际温度数值,铜片夹扣键合产品的工作升温比引线框架少11℃左右。

2.4 夹扣键合封装技术提升器件板级可靠性

CTE(热膨胀系数)不匹配问题是导致SMT 元器件在线路板上焊点开裂的主要原因[5]。铜片夹扣键合结构各材料特性如表4 所示,其中硅芯片CTE 为2.6×10-6/℃-1,塑封材料CTE 为9×10-6/℃-1,铜片夹扣键合与LDF CTE 为17×10-6/℃-1,相较于其他的QFN 结构,其芯片上增加一层铜材,塑封体整体CTE 趋向于17×10-6/℃-1,一般PCB 材料的CTE 在16×10-6~17×10-6/℃-1之间,这使得产品在温度循环(-40~125 ℃)过程中的CTE 不匹配问题得以减少,从而提升了产品在电路板焊点上的整体寿命。

2.5 夹扣键合封装技术提升了封装效率[6]

铜片夹扣键合封装工艺UPH(单位小时产能)通常是传统多引线键合产品的数倍,以图1 产品为例,键合29 根铜线机台的UPH 通常在600 颗产品左右;而铜片夹扣键合来料为卷盘来料(如图2 所示),通过模具裁切每次贴装20 颗铜片以上,铜片夹扣键合的作业效率可以做到6 000 颗,是多引线键合的10 倍。

3 铜片夹扣键合封装产品设计与工艺介绍

铜片夹扣键合产品基本结构如图3 所示,通过回流焊接的方式,将有特殊形状的铜片焊接于芯片上,实现芯片正面源极与外引脚的互联,铜片夹扣键合产品的原材料是通过腐蚀或冲压工艺制造而成的铜片,其形状与芯片开窗尺寸、芯片厚度、焊接材料厚度以及框架外引脚焊接区尺寸相关,芯片表面需要焊锡可浸润材料,如镍金镀层或镍钯金镀层,设计过程中还需要同步考虑铜片重心、表面张力等因素的影响,避免回流焊接过程中因重力和表面张力等作用导致的铜片位置偏移、旋转等问题。

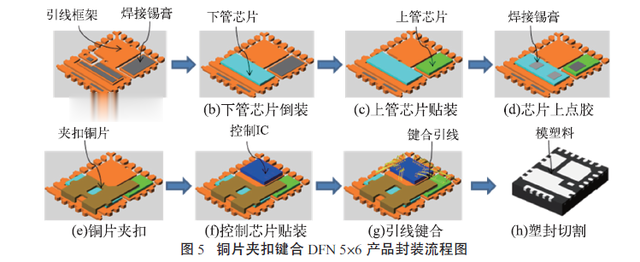

针对高端DRMOS(集成驱动器MOSFET)产品,其封装体中包含3 颗芯片,一颗驱动IC 和两颗MOSFET (其中MOSFET 分为上管MOS 与下管MOS),整个电路构成一个同步降压电路,铜片夹扣键合作为上管芯片与下管芯片互联的重要桥梁,封装结构与电路如图4 所示。

整个产品封装流程为:引线框架点焊料→下管芯片倒装→上管芯片贴装→芯片上点焊料→铜片贴装→回流焊接→助焊剂清洗→IC 芯片贴装→键合→塑封以及后段封装工艺,如图5 所示。芯片与框架焊接,铜片与芯片焊接层材料相同,为锡铅焊料,可选材料有Sn10Pb88Ag2 或者Sn5Pb92.5Ag2.5。这两种材料液相线温度为280 ℃左右,其回流焊接峰值温度在360~400℃之间,业界通用的助焊剂在此峰值温度下会碳化,因此焊接材料助焊剂的选择是产品工艺设计的重中之重,需栅极键合的产品多数选择低残留助焊剂,一般助焊剂回流后残余比例<5%,低助焊剂残余可以避免因为助焊剂污染导致的后期键合失效问题。

4 铜片夹扣键合封装结构与发展

4.1 第一代产品:单芯片铜片夹扣键合封装

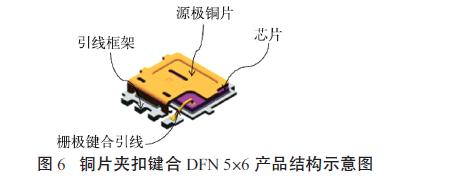

图6 所示为某半导体公司于2010 年推出的DFN5×6 封装产品结构,这种设计被认为是第一代铜片夹扣键合产品,其中芯片厚度为0.2 mm 左右,通过焊料正焊于引线框架上,场效应晶体管芯片源极铜片焊接于引线框架上,芯片栅极通过引线键合焊接于框架上。

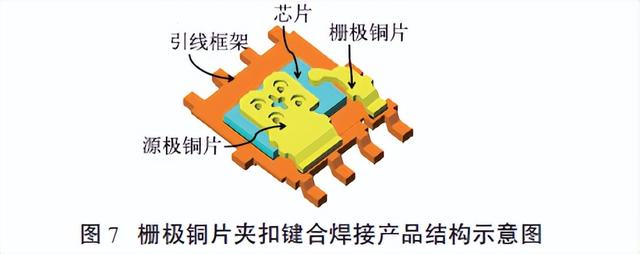

有的设计公司在芯片设计端增大了栅极面积,栅极与源极均采用铜片焊接方式,如图7 所示,这种设计在封装工艺中减少了一步引线键合工艺,降低了封装成本,但因增大栅极面积导致产品芯片利用率降低,因此提升了芯片成本。

4.2 第二代产品:双芯片铜片夹扣键合封装

伴随着产品集成度要求的提升,许多公司推出了多芯片多铜片夹扣键合封装产品,其产品结构如图8所示,其中上管芯片、下管芯片均焊接于引线框架上,通过铜片夹扣键合实现上管芯片源极与下管芯片漏极的串联,上下管芯片栅极均通过铜片焊接于引线框架上,整个产品中包含2 颗芯片、4 个铜片,通过一次回流焊接的方式完成全部互联工作。

2012 年之后,随着倒装工艺的蓬勃发展,也有公司提出了另一种结构设计,如图9 所示,其中上管芯片正焊于引线框架上,下管芯片倒装焊接于特殊设计的框架基岛上,下管芯片漏极与上管芯片源极通过铜片相连,铜片同时焊接于引线框架两边引脚上,这种设计可有效提升铜片面积,降低铜片设计加工难度,同时有助于产品散热,这种产品现在被广泛应用于各种服务器类电源管理同步降压器件中,部分产品可做到峰值效率95%以上。

4.3 第三代产品:多芯片铜片夹扣键合DRMOS 封装

DRMOS 技术是Intel 在2004 年推出的服务器主板节能技术,是将传统MOSFET 供电中分离的两组MOS 管和驱动IC 以更加先进的制程整合在一片芯片中,它的加入能够让服务器在工作时更稳定、更节能。三合一封装的DRMOS 面积是分离MOSFET 的1/4,功率密度是分离MOSFET 的3 倍[7],用铜片夹扣键合替换传统引线键合,有效提升了DRMOS 产品的通流能力,也有效提升了产品散热能力,对于提升器件的整体效率有一定的帮助。参考双芯片铜片夹扣键合产品发展方向,一种集成倒装焊接与铜片夹扣键合焊接为一体的DRMOS 产品也被开发出来,其封装结构如图3 所示,其中上管、下管芯片通过铜片互联,下管芯片倒装于特殊结构设计的引线框架上,IC 芯片仍采用引线键合方式互联。这种设计成为当前最主流的DRMOS 产品结构,产品尺寸从QFN 5×4 发展到QFN5×6。另外美国AOS 公司还设计了一种将IC 堆叠于铜片上的DRMOS 结构,这种设计将器件总面积缩小到QFN 5×3.5,是目前为止最小的DRMOS 铜片夹扣键合产品[8]。

5 铜片夹扣键合封装技术展望

集成电路的发展一直围绕着高集成度、高散热、高效率、低成本4 个方面进行,铜片夹扣键合产品在这4 个方面有着得天独厚的优势,尤其在高集成度、高散热方面,其封装内部结构通过Clip 的结构设计可以做到多样化设计,如芯片堆叠工艺、铜片堆叠工艺,另外因铜片夹扣键合产品的结构特殊性,其封装元件可实现双面散热工艺,将铜片外漏于封装体表面,提升元件的散热能力。随着集成度的不断提升,其最终也会被应用于SIP 类系统级封装器件中,而伴随着封装元器件对于通流能力要求的增加,芯片封装尺寸也随之增大,铜片夹扣键合工艺也会被用于超大芯片封装中。针对铜片夹扣键合封装工艺的开发,目前国外许多知名功率器件产品公司都围绕着这3 个方面进行着开发工作,但其产品工艺良率以及产品可靠性尚无法满足客户需求。

5.1 夹扣键合封装的双面散热

通过封装工艺将芯片表面焊接的散热片从封装体中裸露出来,制作出一种双面散热片类型的封装形式,如图10 所示,通过贴装散热片等方式提升器件散热能力,其工艺难点在于散热片外漏的工艺方法。第一种方法是在塑封模具顶部增加离型膜,封装过程中通过薄膜覆盖保护铜片正面,避免塑封材料覆盖于铜片表面,从而实现铜片的外漏。这种方法操作简单,便于大批量制作,其缺点是产品内部会受到合模压力的影响,会导致芯片开裂、器件失效等问题。第二种方法是产品塑封仍采用传统塑封结构,塑封料覆盖于产品表面,最后通过研磨的方式将塑封料去除,实现铜片外漏于塑封体外。相较于第一种方法,这种工艺流程对于产品内部损伤小,可有效避免芯片开裂等问题,其缺点在于成本较高。

夹扣键合双面散热产品外漏的铜片表面可以再次贴装散热片,如图11 所示,因此铜片夹扣键合双面散热塑封体表面除了能提升器件的被动散热能力以外,还可以提升其主动散热能力,通过增加风扇实现主动散热,可以有效降低器件温度20%以上,而期间工作温度降低可以有效提升元器件的整体寿命[9]。

5.2 SIP 系统级封装

SIP 封装(System in a Package,系统级封装)是将多个具有不同功能的有源电子元件与可选无源器件组装到一起,实现一定功能的单个封装件,从而形成一个系统或者子系统。如图12 所示,产品内部除DRMOS 器件所包含的芯片以及铜片以外还集成了电容、电阻元件,这种结构在板级应用端可有效减少阻容元件占板面积,提升SMT 效率,因为多种器件的结合,元器件整体效率与散热问题成为这种封装结构的瓶颈问题[10],而铜片夹扣键合可以有效解决这些问题。不过因为产品结构复杂,不同工艺过程需要不同的作业温度,而且阻容元件也有其自身耐温特性,常见电容元件能承受的最高作业温度为260℃,所以铜片夹扣键合中常见的高铅焊料变得不合时宜。目前这种产品的开发主要围绕着材料方面进行,常见的选择方向是锡锑合金焊料,其熔点为250℃,焊接工艺温度可以控制在260℃以内,其缺点是工艺温度控制困难,回流焊接空洞较大。另一种材料为烧结银材料,这种材料的优点是可以通过低温烘烤进行烧结,通常作业温度为230℃,同时这种材料有着较高的耐温特性与可靠性[11],其缺点是材料成本较高。

5.3 超大芯片铜片夹扣键合封装

当前市场上铜片夹扣键合产品量产封装元器件尺寸均在DFN 6 mm×6 mm 以下,其封装芯片尺寸小于4 mm×4 mm,当芯片尺寸增大时,铜片焊接面积也随之增大,但铜片与芯片之间的CTE(热膨胀系数)不匹配问题却变得越来越明显,这部分应力会导致元器件的焊接层开裂问题,如图13 所示,-60 ℃到150 ℃温度循环测试500 次循环后,芯片焊锡层开裂。

封装工艺中解决焊接材料开裂的方法主要集中在两个方面,第一种方法是在材料方面着手改善工作,例如提升材料抗蠕变特性,将锡铅焊料替换成纳米银烧结材料,或者改变塑封材料CTE 用以配合产品结构的综合CTE 特性。第二种方法是改变设计结构,通过不同的设计结构来提升产品温度循环寿命,最简单的方法是提升焊接层厚度。为了提高器件的可靠性,焊接层厚度越大越好[12],通过一些特殊的凸包设计可以有效提升焊接层厚度,如图14 所示,通过在铜片上增加25μm凸包设计可以将焊锡层厚度控制在25μm 以上。

6 总结

铜片夹扣键合在同步降压电路中相较于传统的引线键合器件有着高效率、高散热性能、高可通电流、低成本等优点,随着铜片夹扣键合工艺的不断推陈出新,其未来也会成为功率元件的重要发展方向。

论文通过对比与描述的方法在电流承载能力、导通电阻、器件热阻、板级可靠性以及加工效率等多方面对铜片夹扣键合器件的优势进行了详细分析,同时对不同阶段铜片夹扣键合器件的结构发展与功能拓展进行了总结,也总结了铜片夹扣键合未来发展的3个方向———双面散热、系统级封装、超大芯片铜片夹扣键合封装设计与工艺方面当前存在问题,同时针对存在问题给出了相应的解决策略。

铜片夹扣键合工艺在国内还处于初期摸索阶段,在产品结构设计以及封装工艺设计中,未来还会面临各种各样的挑战,随着国内设计公司市场领域的不断扩展,这种封装工艺带来的产品性能优势将变得更加明显,其封装工艺与产品可靠性的开发与研究工作也变得越来越重要。