一、IBM Telum芯片概要

IBM 在2021年 HotChips 上发布了 IBM Telum 处理器;Telum 成为下一代 IBM Z 和 LinuxONE 系统的中央处理器芯片。

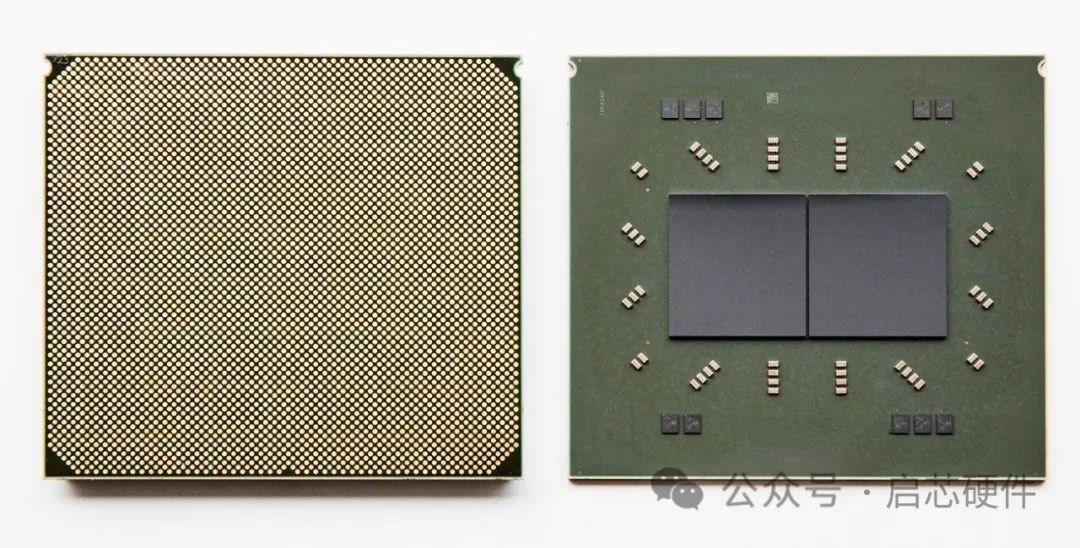

Telum 比 z15 更简单——它是一款基于三星 7nm 工艺构建的八核处理器,每个封装上组合了两个处理器(类似于 AMD Ryzen 的小芯片方法)。

前身 IBM z15 芯片旨在为 IBM Z 和 LinuxONE 系统提供业界领先的七个 9 可用性。Telum 旨在通过关键创新进一步提高可用性,包括重新设计的 8 通道内存接口,能够承受整个通道或 DIMM 故障,并设计用于透明地恢复数据而不影响响应时间。

Telum 添加了新的集成 AI 加速器,每个芯片的计算能力超过 6 TFLOPs。每个核心都可以访问AI加速器,并且可以动态地利用整个计算能力来最大限度地减少推理延迟。由于集中式加速器架构直接连接到缓存基础设施,Telum 旨在为响应时间敏感的工作负载实现极低延迟的推理。计划系统支持高达 200 TFLOP,AI 加速还旨在扩展以满足最苛刻的工作负载的要求。

Telum 的工作原理

在诸如CPU之类的传统计算系统中,计算是通过在存储器和处理器之间重复传输指令和数据来执行的。但人工智能工作负载的计算要求要高得多,并且需要处理大量数据。因此,当您将 AI 融入应用程序工作流程时,拥有一个由 CPU 和 AI 内核组成的异构系统至关重要,这些系统紧密集成在同一芯片上,以支持极低延迟的 AI 推理。

Telum 正是实现了这一目标,除了传统的 CPU 性能之外,还为未来的 IBM 系统提供了专用的 AI 资源。CPU 内核可有效用于通用软件应用程序,AI 内核可高效运行深度学习工作负载,并且两种类型内核的紧密耦合有助于促进快速数据交换。

Telum 沿袭了 IBM 的全栈系统设计方法的历史,即针对客户最关键的工作负载共同优化芯片技术、硬件、固件、操作系统和中间件。借助 Telum,客户每秒可以处理数以万计的人工智能交易。

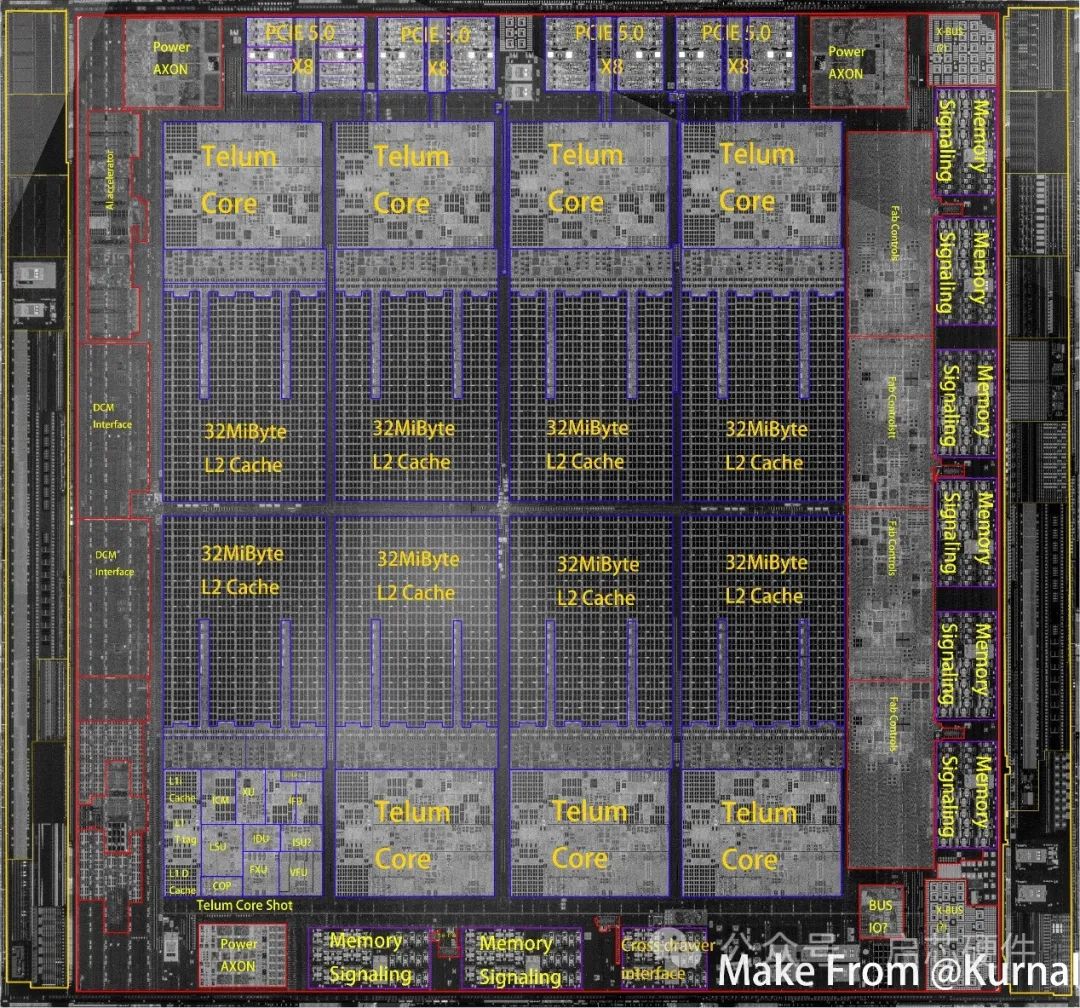

二、Telum的 die floorplan 基本介绍

IBM Telum芯片的floorplan如下图所示

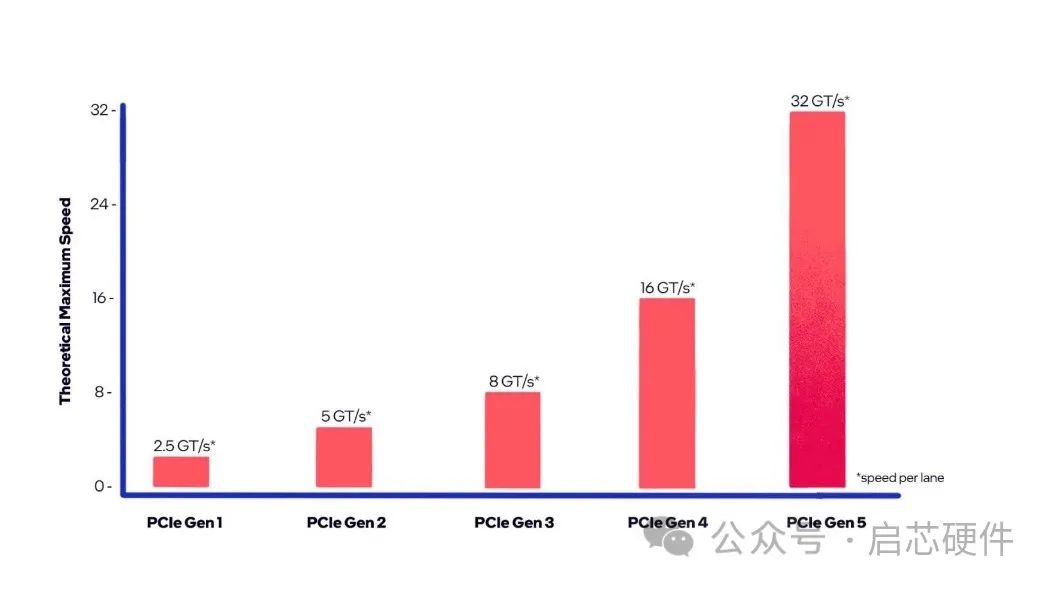

1.PCIe 模组,最上方为PCIe 5.0, X8规格,一共四个,理论上能提供的传输速率为32GT/sx8x4=1024GT/s

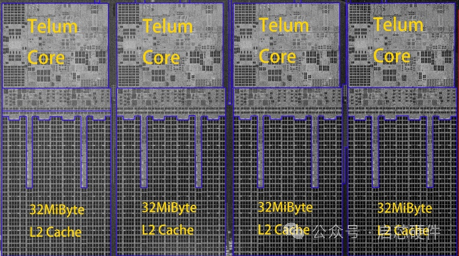

2.Telum core和缓存。正下方是8组telum core和L2缓存,采用4上4下的mirror摆放,组成8 core+8 cache的结构。值得注意的是有一个超大的L2 Cache, 达到了32MB, 要知道一般同类芯片L2 可能只有1MB左右。

3.DDR模组。其中一个如下图,一共4组,为DDR5规格。

Telum是一种新一代的芯片,能看出一些 power 的影子,但是确实不完全是 power,偏向于银行和加密需求。它的缓存设计取消了L3和L4,用巨大的L2代替,可以将数据存储在其他核心、基板、组或单元的空闲L2内。除此之外,Telum还拥有4通道ddr5、x8x4pcie5.0和一堆AI加密单元。

高速缓存是每个微处理器的关键设计组件,对处理器的整体性能影响巨大。缓存就像存储柜,可以在处理器的前门存储数据,或者提前缓存数据。

这对于当今运行速度如此之快(通常以许多千兆赫的速度)的处理器来说尤其重要,以至于每当系统需要等待数据时,宝贵的时钟周期就会被浪费。

Telum 取消了 L3,L4,用巨大的 L2 来代替,这样设计会导致其缓存具有巨大的访问延迟,但是 telum 很神奇,其将以前放置在 L3 的数据放在其余空余核心的 L2 内,L4 同理,导致其意义上,一个 chip 物理有 256M 的 L2 (8X32), 但是单个核心可以读取核心外的 32M l2,256M L3,以及一整个复合体(整个 ibm z16?单元)的 32mx8 核 x2(2die 封装一个 sub)x16 的 8GB 的 L4,说明白点,一个核心数据存不下了可以放在其他核心,不同基板,甚至不同组或者不同单元的 L2 内,只要是空闲的。

三、Telum的 dieshot细节分析

Telum微处理器包含 8 个处理器核心,主频超过 5GHz,每个核心均由重新设计的 32MB 专用二级缓存支持。二级缓存交互形成256MB虚拟三级缓存和2GB四级缓存。除了处理器内核本身的改进之外,每个内核的缓存比 z15 一代增长了 1.5 倍,旨在显着提高 IBM 在下一代 IBM Z 系统中提供的每线程性能和总容量。Telum 的性能改进对于复杂交易系统的快速响应时间至关重要,尤其是在实时人工智能推理的增强下。

该芯片还包含 220 亿个晶体管和 17 个金属层上 19 inch的走线。Telum由三星制造,采用7nm EUV技术节点开发。

IBM 院士Christian Jacobi表示:“我们对 Telum 芯片所做的就是完全重新设计了这些缓存的工作方式,使更多的数据比过去更靠近处理器核心。” IBM zSystems 系统架构和设计首席技术官。“为此,我们将二级缓存增加了四倍。我们现在拥有 32 MB 的二级缓存。”

L2 缓存的这个大小与大多数其他服务器芯片形成鲜明对比,其他服务器芯片的缓存大小约为半兆字节或 1 MB。为了使这个更大的 L2 缓存有效工作,IBM 优化了访问模式以及处理器核心如何访问非常大的 32 MB 缓存(八个核心为 256 MB),从而使其具有极低的延迟。

“我们不再受控制逻辑的限制,控制逻辑要确定数据在缓存中的实际位置,然后将请求发送到缓存的正确扇区并缓慢移动数据,”Jacobi 说。“我们的设计方式是,我们真正只受到电传输延迟的限制,以获取数据、触发从阵列中读取数据,然后将其流回需要的地方。”

四、总结

Telum 芯片之前的一代芯片采用四级高速缓存:最接近的一级高速缓存是一级 (L1),下一级是二级 (L2),依此类推,直到达到四级 (L4)。传统上,缓存层次结构是在芯片上构建 L1、L2 和 L3,而 L4 则在芯片外构建。每个级别的大小都会随着您的推移而增加,并且它们距离处理器引擎本身越远,延迟也会增加。

IBM Telum Dieshot,图片来自 IBM 官网,制作 / 绘画来自 Kurnal