摘要

目前SiC 产业正由 150 mm(6 英寸)向 200 mm(8 英寸)转型,为满足行业对大尺寸、高质量 SiC 同质外延片的迫切需求, 采用自主研制的 200 mmSiC 外延生长设备在国产衬底上成功制备出 150 mm、200 mm 4H-SiC 同质外延片,并开发了适用于 150 mm 及 200 mm 的同质外延工艺,其中 外延生长速率可大于 60 μm/h,在满足高速外延的同时,外延片质量优异,其中 150 mm、200 mm SiC 外延片厚度均匀性都可控制在 1.5%以内,浓度均匀性均小于 3%,致命缺陷密度小于 0.3颗 /cm2 , 外延表面粗糙度均方根 Ra 小于 0.15 nm,各核心工艺指标均处于行业先进水平。

碳化硅(Silicon Carbide,SiC)是第三代半导体材料的代表之一,具有击穿场强高、热导率性能优、 电子饱和漂移速度大、抗辐射能力强等特点,大幅扩展了功率器件的能量处理能力,可满足下一代电力电子装备对器件大功率、小体积和高温、高辐射 等极端条件的服役要求,可缩小空间、减少功耗和 降低冷却要求等优势,已经为新能源汽车、轨道交通、智能电网等领域带来了革命性的变化。因此, 碳化硅半导体已成为公认的将引领下一代大功率 电力电子器件理想材料。近年来,得益于国家对第三代半导体产业发展的政策支持,目前国内 基本完成了 150 mm SiC 器件产业体系的研发与建设,产业链安全得到了基本保障。因此,行业关 注点逐渐向成本控制、效率提升方向转型。由表 1 可知,相较于 150 mm,200 mm 碳化硅边缘利用率更高,单片晶圆芯片产出数量可提高约 1.8 倍, 技术成熟后单颗芯片制造成本可 下降 30% , 200 mm 的技术突破是“降本增效”的直接手段, 也是我国半导体产业走向“并跑”甚至“领跑”的关键。

与 Si 器件工艺有所区别的是,碳化硅半导体功率器件都是以外延层为基石加工制备而成,外延 片是碳化硅功率器件必不可少的基础材料,外延层 的质量直接决定器件的良率,其成本占芯片制造成 本的 20%,因此,外延生长是碳化硅功率器件中必 不可少的中间环节。外延工艺水平上限由外延装备决定,目前国内 150 mm SiC 外延装备国产化程 度较高,但 200 mm 布局整体落后于国际同期水 平,因此,为解决国内第三代半导体产业发展对大 尺寸、高质量外延材料制造的迫切需求和瓶颈问题,本文介绍了我国成功研制的 200 mm SiC 外延 装备,并对外延工艺进行了研究,通过优化工艺温 度、载气流量、C/Si 比等工艺参数,在自主开发的200 mm 碳化硅外延炉上获得了浓度均匀性 <3%, 厚度不均匀性 <1.5%,粗糙度 Ra<0.2 nm 以及致命 缺陷密度 <0.3 颗 /cm2 的 150 mm、200 mm SiC 外 延片,设备工艺水平可满足高质量 SiC 功率器件制备需求。

1 实验

1.1 SiC 外延工艺原理

4H-SiC 同质外延生长工艺主要包括 2 个关键 步骤,即 4H-SiC 衬底的高温原位刻蚀和同质化学气相沉积过程。衬底原位刻蚀主要目的是去除晶 圆抛光后衬底亚表面损伤、残留的抛光液、颗粒物 及氧化层等,并且通过刻蚀可在衬底表面形成规 则的原子台阶结构。原位刻蚀通常在氢气气氛下进行,根据实际工艺需求也可以加入少量辅助气 体,如氯化氢、丙烷、乙烯或者硅烷等,原位氢气刻蚀的温度一般在 1 600 ℃以上,刻蚀过程中反应室压力一般控制在 2×104 Pa 以下。

经过原位刻蚀使衬底表面活化后,进入高温化学气相沉积过程,即通过大流量载气(一般为氢气)将生长源(如乙烯 / 丙烷、TCS/ 硅烷),掺杂源 (n 型掺杂源氮气、p 型掺杂源 TMAl),辅助气体 如氯化氢等输送至反应室,气体在高温反应室内 发生气相反应后,部分前驱体在晶圆表面发生化 学反应并吸附,以单晶 4H-SiC 衬底为模板,在衬底表面形成特定掺杂浓度、特定厚度、更高质量的单晶同质 4H-SiC 外延层。历经多年的技术摸索, 目前 4H-SiC 同质外延技术已基本成熟,并大规模应用于工业化生产中 。国际上应用最广泛的 4H-SiC 同质外延技术具备 2 个典型的特征:(1) 以偏轴(相对〈0001〉晶面,朝〈11-20〉晶向)斜切衬 底为模板通过台阶流的形式 (Step-flow growth mode)在衬底上沉积无杂相的高纯单晶 4H-SiC 外 延层。早期的 4H-SiC 同质外延采用正晶向衬底, 即〈0001〉Si 面进行生长。正晶向衬底表面原子台 阶的密度低,且台面宽,外延过程中容易出现二维成核生长形成 3C 晶型 SiC(3C-SiC)。通过偏轴切 割可以在4H-SiC〈0001〉衬底表面引入高密度、窄台面宽度的原子台阶,吸附的前驱体能够通过表 面扩散有效地达到表面能相对较低的原子台阶位 置。在台阶处,前驱体原子 / 分子团成键并入位置是唯一的,因此在台阶流生长模式下,外延层可完 美继承衬底的 Si-C 双原子层堆垛序列,形成与衬底晶相相同的单晶。(2)通过引入含氯硅源实 现高速外延生长。在常规 SiC 化学气相沉积系统 中,硅烷和丙烷(或者乙烯)是主要的生长源。在通过加大生长源流量提高生长速率过程中,随着硅组分平衡分压不断提高,容易发生气相同质成核形成硅团簇,显著降低硅源利用率,硅团簇的 形成极大程度上限制外延生长速率的提升,同时硅团簇可对台阶流生长产生扰动,导致缺陷成核。为了避免同质气相成核,提高外延生长速 率,引入氯基硅源是目前提高 4H-SiC 外延速率 的主流方法。

1.2 200 mm(8 英寸)SiC 外延设备与工艺条件

本文所述实验均是在中国电子科技集团公司第四十八研究所自主研制的 150/200 mm (6/8 英 寸) 兼容的单片式水平热壁 SiC 外延设备上进行的。该外延炉支持全自动晶圆上下料,图 1 为外延设备反应腔内部结构简图,由图 1 可知,反应腔外 壁为带水冷夹层的石英钟罩,钟罩内部则是高温反应室,该反应室由保温碳毡、高纯特种石墨腔、石墨 类气浮旋转基座等组成。整个石英钟罩外部套有圆 柱形的感应线圈,通过中频感应电源对钟罩内部反应室进行电磁感应加热。如图 1(b)所示,载气、反应气体以及掺杂气体等均有反应室上游以水平层 流的方式流过晶圆表面到达反应室下游,由尾气端 排出。为保证晶圆片内一致性,在工艺过程中由气 浮基座所承载的晶圆始终保持旋转。

实验所用衬底为山西烁科晶体生产的商用 150 mm、200 mm (6 英寸、8 英寸)<1120> 方向 4°偏角导电 n 型 4H-SiC 双面抛光 SiC 衬底。工艺实验中使用三氯氢硅 (SiHCl3,TCS) 和乙烯 (C2H4 )作为主要生长源,其中,TCS 和 C2H4 分别作 为硅源和碳源,高纯氮气(N2 )作为 n 型掺杂源,氢 气(H2 )作为稀释气体及载气。外延工艺温度范围为 1600 ~1660 ℃,工艺压力为 8×103 ~12×103 Pa, H2载气流量为 100~140 L/min。

1.3 外延片测试与表征

采用 Fourier 红外光谱仪 (设备厂家 Thermalfisher,型号 iS50 以及汞探针浓度测试仪(设备厂家 Semilab,型号 530L)分别对外延层厚度、掺杂浓度 的均值以及分布进行了表征;外延层片内各点厚度 及掺杂浓度按照去边 5 mm,沿与主参考边法线在 晶圆中心点呈 45°相交直径线取点,150 mm 晶圆 单条直径线取 9 点(两条直径互相垂直),200 mm 晶圆则取 21 点,如图 2 所示。采用原子力显微镜(设 备厂家 Bruker,型号 Dimension Icon)分别在外延片 中心区域和靠边缘区域(去边 5 mm)选取 30 μm× 30 μm 面积对外延层表面粗糙度进行测试;外延 层缺陷则是采用表面缺陷测试仪 (设备厂家中电 科风华,型号 Mars 4410 pro)进行表征。

2 实验结果与讨论

2.1 外延层厚度及均匀性

外延层厚度、掺杂浓度及其均匀性是判断外 延片质量的核心指标之一,精确可控的厚度、掺杂 浓度及片内均匀性是保障 SiC 功率器件性能及一 致性的关键,而外延层厚度及掺杂浓度均匀性也 是衡量外延设备工艺能力的重要依据。

图 3 为 150 mm、200 mm SiC 外延片的厚度 均匀性及其分布曲线图。由图可知,外延层厚度分 布曲线以晶圆中心点呈左右对称关系。外延工艺 时间为 600 s,150 mm 外延片外延层厚度平均值 为 10.89 μm,厚度均匀性为 1.05%,通过计算,外延生长速率为 65.3 μm/h,是典型的快速外延工艺水平。在相同外延工艺时间下,200 mm 外延片外 延层厚度为 10.10 μm,厚度均匀性为 1.36%以内,整体生长速率为 60.60 μm/h,略低于 150 mm 外延生长速率,这是因为硅源和碳源从反应室上 游流经晶圆表面到达反应室下游时存在明显的沿 程损耗,而 200 mm 晶圆面积比 150 mm 更大,气体流过 200 mm 晶圆的表面距离更长,沿程损耗 消耗的源气更多,在晶圆保持旋转的条件下,外延层总体厚度更薄,从而生长速率更慢。整体而言, 150 mm 及 200 mm 外延片厚度均匀性优异,设备 的工艺能力能满足高质量器件的要求。

2.2 外延层掺杂浓度及均匀性

图 4 为 150 mm、200 mm SiC 外延片掺杂浓度均匀性以及曲线分布。由图可知,外延片上浓度分布曲线相对于晶圆中心具有明显的对称性,150 mm、200 mm 外 延 层 掺 杂 浓 度 均 匀 性 分 别 为 2.80% 和 2.66%,均能控制在 3%以内,为国际同类型设备的 优异水平。外延层掺杂浓度曲线分布沿直径方向为 “W”型分布,这主要是由水平热壁式外延炉流场决定,因为水平气流式外延生长炉气流方向是由进气端(上游)流入,并经过晶圆表面以层流的方 式从下游端流出;由于碳源(C2H4 )的“沿程耗尽” 速率高于硅源(TCS),在晶圆旋转的情况下,晶圆 表面的实际 C/Si 由边缘至中心逐渐递减(中心位 置的碳源较少),根据 C、N 的“竞位理论”,晶 圆中心的掺杂浓度逐渐向边缘递减,为得到优异的 浓度均匀性,外延过程中通过额外增加边缘 N2 作为补偿,以减缓掺杂浓度由中心至边缘的下降幅度,进而使最终的掺杂浓度曲线呈现“W”型。

2.3 外延层缺陷

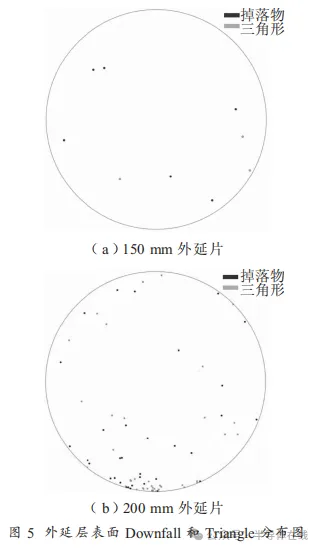

除了厚度、掺杂浓度以外,外延层缺陷控制水 平也是衡量外延片质量的核心参数,也是体现外延 设备工艺能力的重要指标。虽然 SBD 及 MOSFET 对缺陷的要求有所区别,但较为明显的表面形貌缺 陷如掉落物缺陷、三角形缺陷、胡萝卜缺陷、彗星缺 陷等都同时被定义为 SBD 及 MOSFET 器件的致 命缺陷(Killer defect),含有这些缺陷的芯片失效概 率大,因此控制致命缺陷的数量对提高芯片良率、降低成本极为重要。图 5 为 150 mm、200 mm SiC 外延片致命缺陷分布图,在 C/Si 比不存在明显失衡 的条件下,胡萝卜缺陷及彗星缺陷基本可以消除,而 掉落物缺陷、三角形缺陷与外延设备运行过程中洁 净度控制、反应室石墨件杂质水平以及衬底质量有 关。从表 2 可知,150 mm、200 mm 外延片致命缺陷 密度均能控制在 0.3 颗/cm2 以内,为同类型设备优 异水平。150 mm 外延片致命缺陷密度控制水平优于 200 mm 外延片,这是因为 150 mm 衬底制备工艺比 200 mm 更成熟,衬底质量更好,且 150 mm 石墨反 应室杂质控制水平更优异而产生的现象。

2.4 外延片表面粗糙度

图 6 分别为 150 mm 及 200 mm SiC 外延片 表面的 AFM 图像。从图中可以看出,150 mm、 200 mm 外 延 片 表 面 均 方 根 粗 糙 度 Ra 分 别 为 0.129 nm 和 0.113 nm,且外延层表面光滑,没有明 显的巨观台阶( Macro-step) 聚集现象,该现象表明 整个外延过程中外延层的生长始终维持台阶流生 长模式,没有发生台阶聚集。由此可知,采用优化后的外延生长工艺,均可在 150 mm 及 200 mm 低偏 角衬底上获得光滑表面的外延层。

3 结论

采用自主研制的 200 mm SiC 外延生长设备 在国 产衬底 上 成功 制备 了 150 mm 及 200 mm 4H-SiC 同质外延片,并开发了适用于 150 mm 及 200 mm 的同质外延工艺,其中外延生长速率可大 于 60 μm/h,在满足高速外延的同时,外延片质量 优异,其中 150 mm 及 200 mm SiC 外延片厚度均 匀性可控制在 1.5%以内,浓度均匀性均小于 3%,致命缺陷密度小于 0.3 颗 /cm2 ,外延表面粗糙度 均方根 Ra 小于 0.15 nm,外延片各核心工艺指标 均处于行业先进水平。

来源:电子工业专用设备;宽禁带半导体技术创新联盟

作者:谢添乐,李 苹,杨 宇,巩小亮,巴 赛,陈国钦,万胜强

半导体工程师

半导体经验分享,半导体成果交流,半导体信息发布。半导体行业动态,半导体从业者职业规划,芯片工程师成长历程。