在芯片设计过程中有时需要对特殊端口进行ESD防护设计,例如正负电压输入、大幅信号输入、高压IO、信号完整性等需求。这些特殊端口的ESD防护设计一直都是重难点。这一期对高压端口的ESD防护进行简单概述(这里的高压是指20V~120V)。

一.器件设计

高压工艺普遍都是BCD工艺,而且为了提高器件耐压能力,fab会应用到诸如Resurf、场板、Super Junction等技术。

体隔离BCD工艺还需留意器件的隔离设计(SOI工艺在隔离上优势很大)。总的来说HV的ESD防护设计难度更大但是发挥空间也大,更能天马行空。

关于HV ESD Device的设计主要有两种设计思路,一种是设计耐高压的单体器件,这种设计思路不确定性大,结构复杂,设计难度高,但是面积较小,且一致性好。另一种是采取堆叠设计,将低压ESD器件进行堆叠实现对高压端口的防护,这种思路对器件的隔离性能有较高要求,且面积需求大,但是性能稳定,可靠性高。两种思路各有千秋,需要根据场景选择合适的方案。

1.1单体器件

1.1.1 Reverse Diode

反偏二极管作为ESD防护器件一般应用于三极管工艺,这类工艺下反偏PN结雪崩击穿后还能保持泄放能力并不会直接被热击穿,而且内部器件的鲁棒性也足够优秀,无需考虑残压残流的影响。所以能直接用反偏二极管作为ESD防护器件。

1.1.2 Bipolar

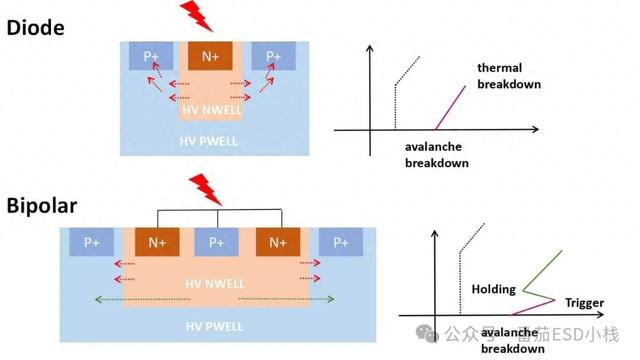

图一.Diode与Bipolar的ESD区别。

如图一所示,ESD防护器件中Bipolar与Diode的区别在于雪崩击穿后,二极管只能继续通过阳极持续泄放,直到器件失效,而三极管在雪崩击穿后会产生一个基级电位,从而协助开启整个三极管,三极管开启后因为存在电流放大倍数,整个器件的泄放能力得到增强,表现出Snap-Back特性。所以Bipolar从雪崩击穿转变为热击穿的裕度更大,其泄放能力强于Diode。Bipolar分为Vertical和Horizontal两种结构,每种结构的ESD特性有所区别,且为了提高耐压能力,有些Bipolar中也会应用Resurf技术,这使得Bipolar的技术细节千变万化。这一期只是概述,后续会针对具体技术细节展开讨论。

图二.Vertical Bipolar和Horizontal Bipolar的示意图。

1.1.3 GGLDNMOS

LDMOS作为耐高压的MOS器件,其也能同NMOS一样将栅极接地进行ESD防护

1.1.4 HV Diode SCR

针对HV端口的ESD防护,如图三所示,可以将HV Diode改进成为SCR,在HV Diode的HV NweLL中插入P+,在HV PweLL中插入N+,HV NweLL/HV PweLL作为SCR的主结,HV NweLL作为阳极, HV PweLL作为阴极。HV Diode SCR的Holding Voltage 相对于工作电压还是较低,很容易有LU风险,但是过度削弱器件的Snap-Back特性除了会降低器件的Trigger Voltage,还会降低器件鲁棒性,所以只能抬高器件的Holding Current,增大寄生三极管的内阻,以此降低器件误触发的几率。从TLP曲线中看出。两者的雪崩击穿电压一致,雪崩击穿后Diode一直维持正电阻特性,而SCR触发负电阻特性,泄放效率上SCR远高于Diode。因为高压工艺在制备高压阱时受推结深度,推结浓度等影响导致BreakDown Voltage的Min与Max相差较大,且设计不当可能导致雪崩击穿直接演变为热击穿。所以HV Diode SCR的稳定性较差。

图三.HV Diode与HV Diode SCR的示意图。

1.1.5 LDMOS_SCR

该设计思路是以LDMOS为蓝本改进成为SCR。如图四所示,在NLDOMOS的Drain端插入P+作为SCR的阳极,LDMOS的Source端作为阴极,图中列出了四种不同的版图结构,a).只加P+和N+,b).取消BN埋层,c).增加BN埋层,d).有源区交叉版图,从TLP上看a与d的鲁棒性最佳,a与b的Trigger Voltage最高,a的Snap-Back最深。

LDMOS_SCR的泄放效率远高于GGNLDMOS,LDMOS_SCR在漂移区发生雪崩击穿后,寄生的NPN和PNP开始相互耦合,触发Snap-Back的效率更快,从而高效缓解漂移区的热电效应,而GGNLDMOS只能靠寄生NPN泄放ESD,热电效应消散较慢,相比之下LDMOS_SCR能很大程度的避免漂移区对ESD泄放效率的影响,LDMOS_SCR这一技术的特点就是一致性好,LDMOS与LDMOS_SCR的工艺漂移是一致的,虽然不能避免漂移,但是漂移保持一致的话也能减少影响(差模思想)。GGNLDMOS与LDMOS_SCR的TLP如图所示,两者的Breakdown Voltage几近一致,Trigger Voltage相差无几,发生Snap-Back前,两者的曲线基本一致,但是Trigger之后LDMOS_SCR的Snap-Back更深,Holding Voltage/Current更低一些,其泄放能力更强。

图四.LDMOS_SCR结构与TLP示意图。

HV-WeLL普遍深度较大,浓度较低,而且受制于推结工艺,HV-WeLL并不一定能处处保持浓度均匀,面对ESD时器件会触发不均匀,所以上述四种器件TLP曲线的漏电流比较“曲折”。下面介绍的这种设计思路便能规避这一问题,让器件更加稳定。

1.1.6 Soft Trigger

Soft Trigger是一种ESD器件的设计思路,该设计分为触发器件和泄放器件,前文所述ESD器件都是靠雪崩击穿开启寄生三极管,但是高压器件的雪崩击穿较难掌控,可以通过触发器件协助泄放器件开启寄生三极管,从而实现对泄放器件参数的精确控制。如图五所示为PMOS Soft Trigger的SCR,PMOS优先触发后,将SCR的N-WeLL和P-WeLL中注入电流,SCR不用发生雪崩击穿即可触发寄生NPN和PNP,其TLP如图所示,第一次Snap-Back是PMOS触发造成的,PMOS触发后电流进入SCR的N-WeLL和P-WeLL中,然后SCR发生第二次Snap-Back。与没有PMOS Soft Trigger的SCR相比,PMOS_SCR的Trigger Voltage低于SCR,而且PMOS是低压器件,其击穿电压较稳定,漏电流也不会出现曲折现象。两者的Holding Voltage相差不大,在触发之后PMOS_SCR和SCR的工作机理便相差无二了。

图五.PMOS Trigger SCR结构与TLP示意图。