今天国产3nm芯片正在开发中的新闻激起千层浪 , 这无疑给了国内半导体市场一剂强心针 , 针对这篇报导 , 咱们就来唠唠 , 国产3nm工艺制程到底靠普不靠普?

经常看作者文章应该对所谓国产5nm这类消息波澜不惊 , 因为早在去年就已经剧透 , 2024年下半年会有N+3 甚至良率分析与产能数据都跟大家分享过 , 今天该报导则更为劲爆 , 上来直接喊3nm , 好像5nm已经不足以吸引眼球 .

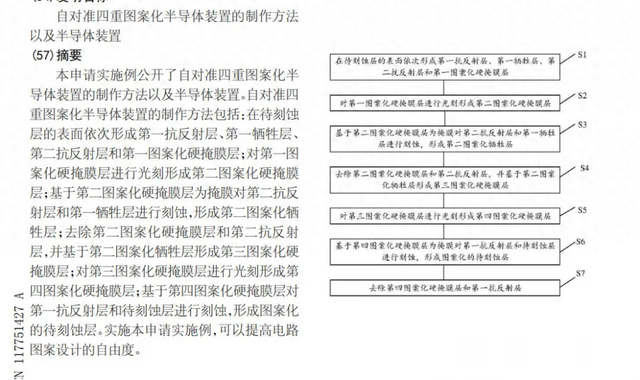

先看看这篇引用Tom’s Hardware报导的细节 , 首先提到了SAQP芯片专利 , 这是今年初公布的 , 市场早在年初沸腾过一番 , 作者之前文章就提过 , 年初这SAQP只是单纯描述了8年前Intel与台积电就在使用的技术 , 没有看出2024的新专利跟之前有什么优化与不同 , 这一点是比较让人失望的

把年初这SAQP专利旧事重提 , 并夸张的挂钩到3nm制程 , 很明显是博眼球手段 , 因为依照行业技术来看SAQP(四除曝光)是能做到7/5nm , IMEC则在去年发布了SAOP(八重曝光)做5/3nm的路线方案 , 也就是说DUVi + SAQP根本达不到3nm , 这属于媒体缺乏基础知识 , 胡乱拼凑各种专业术语的报导 .

浸没式光刻机(DUVi) +多重曝光(Multi-patterning)是十年前未进入EUV时代为了芯片微缩而发展出的技术 , 除了多曝还有许多可以有效降低k1值的RET增益技术 , 诸如OAI或PSM的双光束成像 , 模型OPC校正 , Multi-patterning(LELE、SADP等)都属于RET增益技术 ,

另外还有overEtch , ILT反演光刻 , 甚至最新的DSA技术在不依赖更高分辨率光刻的情况下也能有效生产5nm芯片 , 当然这里面最重要的就是多曝(Multi-patterning) , 因为k1值理论可以减半 , half-Pitch缩减效果最明显 .

该报导也提到了一家公司 , 其最早承担的是设备零部件的开发 , 避免国内企业因进入实体清单拿不到零部件 , 导致Fab中的进口设备停摆 , 后来这家公司更是涉及到了9大半导体设备的整机开发 , 一度因为挖角与业务重叠引发国内设备商大佬在2023年会上PPT专门抨击 .

作者以为 , 做法有待商榷 , 但对于国家来说 , 有竞争是好事 , 做得好就上 , 做不好就下 , 有竞争有压力自然会有更大的动力 , 不过从目前获得的讯息来看 , 这家公司似乎很难在传统半导体设备上与各领域的国产龙头设备商竞争 , 即便这家公司挖了各龙头公司很多人 , 也从海外引入不少顶级高校的华人研究员 , 组织十分豪华庞大 , 但目前的进度似乎不尽人意 , 还是只能在中低端设备与原本的龙头竞争 , 这样的现象 , 充分说明作者一直强调的 , 半导体行业需要不断的技术积累 , 需要时间来产生成果 , 举国之力当然可以加速 , 但也仅仅是加速 , 没办法跳过 , 别人花5年 , 我们举国之力仅仅需要2年或3年 , 但不论2年或3年这也是需要时间 , 没办法直接跳跃式突破 , 更何况我们原本差距并不只是5年 , 半导体任何一个环节都是靠不断努力并加上时间积累而来 , 目前为止我们没有发现这家新公司比其他国产厂家做得更好 .

所谓国产3nm制程必然是与目前的N+2一样 , 完全建立在国内之前取得的进口设备基础之上 , 简单的说 , 就是研究如何用我们手上既有的进口设备去推进更先进的工艺制程 .

目前我们可以使用进口设备有效生产N+2 , 至于下一代的N+3 , 甚至未来的N+4 , 利用我们现在手上的进口设备可以做到 , 文章开头阐述了诸如多曝的许多技术 , 这些技术全部都是非EUV做先进制程的方法 , 作者最近正在写一篇如何用DUVi+MP实现5nm的纯技术文章 , 知识星球的粉丝将能先睹为快 .

现在我们用手上的DUVi光刻机可以实现N+2 , +3 , +4 , 但这个N+2/3/4真的就是对应7nm/5nm/3nm的完整的下一代制程节点推进吗?

我在这直接剧透 , 当然不是 , 现在半导体行业各家Fab提出的多少nm几乎不具备参考意义 , 纯属营销手法 , 比如三星早早推出5nm甚至3nm , 但三星这节点跟别人的5nm/3nm一样吗?

众所周知 , 半导体行业进入14nm FinFET立体结构之后就进入等效的概念 , 而非传统多少nm对应多少Half - Pitch , 既然失去了标准 , 厂家自然可以自由定义 , 比如台积电的N16 , N12 , N6 , 三星8LPP , 4 LPP这种非传统节点 , Intel在之前命名吃大亏之后 , 2021之前全面改名intel 4 , intel 3 , 国内厂家更是用N+1 , N+2 , N+3这种完全与多少nm不挂钩的命名方式 , 既然命名已经没有统一标准 , 那又是如何去对比所谓N+2 , 4LPP , intel 4各种不同名字 , 倒底是5nm, 3nm还是多少nm呢?

其实行业内有个好办法可以去比较各家五花八门的命名 , 那就是单位密度 , MTr/mm2(每平方毫米百万晶体管数量) , 一般来说7nm在100MTr/mm2左右 , 三星, 台积电 ,三星甚至国内的N+2都差不多 , 比如与国内N+2一样使用DUVi + SAQP技术的台积电第一代7nm , MTr是91(每平方毫米0.91亿晶体管) , 而N+2是89 , 英特尔密度最高达101 , 各家均在差不多水平 , 只是推出时间不一样 , N+2晚了7年 , 而台积电2019年推出的优化版7nm的N7+已经达到116MTr .

5nm时代 , 台积电5nm的优化版N4P达到180+ MTr , 而三星却从5LPP的127MT提升到4LPP的137 , 三星的5nm几乎仅仅是台积电7nm的再优化版 .

进入3nm阶段三星目前良率还不太高的3GAE也才150+MTr , 远远不如台积电上一代5nm最强版 的180+ , 也就是说三星号称的3nm却达不到台积电5nm的水平 .

这也是为进入5nm时代 , 三星的铁杆客户高通无法再忍受 , 跑到台积电下单的直接原因 , 晶体管密度相差一个世代 , 等于性能相差一个世代 , 继续在三星下单只能是找虐 , 三星可以随便命名节点但高通可没办法陪你一起玩文字游戏 , 对高通来说这可不是开玩笑的生死局 , 当初很多分析者为三星找出许多不明所以的原因去合理化自己的揣测 , 其实压根不需要揣测 , 只要你了解MTr这样的基础常识就能提早预判 , 高通这类厂家未来会怎么选择 , 这类半导体基础常识跟理念就是作者一直强调希望大家理解的 .

同样的情况也会出现在N+3甚至N+4 , 目前作者获得的资料是N+3在120左右的MTr/mm2 , 后年也会有N+4大约是145左右 , 所以它到底是多少nm , 大家可自行比较 .

国内目前被美强力封锁的半导体行业 , 能够突破封锁持续推进先进节点非常难能可贵 , 这是所有从业人员不懈努力的成果 , 即便产能因为进口设备被限制无法大量扩产 , 但持续推进工艺节点 , 让许多国产芯片不会落后主流太多 , 给整个国内半导体行业争取宝贵的时间至关重要 , 尤其是未来最重要的AI芯片 , 首先争取能满足自身的基本需求 , 然后再透过不断投入与时间积累 , 一代一代的优化以及追赶 , 只要坚持不懈 , 有朝一日中国半导体必然可以开创出另外一片天地 .

来源于梓豪谈芯,作者leslie wu

半导体工程师半导体经验分享,半导体成果交流,半导体信息发布。半导体行业动态,半导体从业者职业规划,芯片工程师成长历程。

半导体工程师半导体经验分享,半导体成果交流,半导体信息发布。半导体行业动态,半导体从业者职业规划,芯片工程师成长历程。